GDDR6存储器物理接口是存储控制器和GDDR6存储器颗粒进行数据通讯交互的桥梁,主要负责将存储控制器端的信号(操作指令、读写地址、数据和时钟等)转换为符合存储器接口协议规范(JEDEC250和DFI 3.1)的时序和电平信号(数据率支持最高16Gbps),并以规范的格式从存储控制器端把信号传送到外部存储器,同时接收外部存储器的数据信号,并将其转换为特定的数据格式传送给存储控制器来完成数据交互。

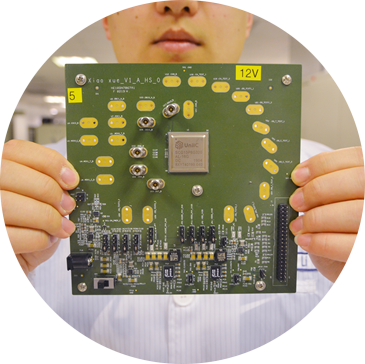

• 已在 Global Foundries 12nm LP FinFet 工艺流片并可提供测试报告.

• 已在 Global Foundries 12nm LP FinFet 工艺流片并可提供测试报告.

• 兼容JEDEC标准no.250 GDDR6 SDRAMs器件.(速率高达16Gbps)

• 内嵌低噪声PLL来满足时序指标.

• 内嵌PVT补偿的延迟链.

• 支持双通道 GDDR6 存储器颗粒.

• 支持回环测试(Loop Back Test)模式.

• 支持QDR和DDR模式的数据传输.

• 支持每八位一组WCK和每十六位一组WCK模式.

• 支持DBI和CABI模式.

• 支持接收器(RX) 判决反馈均衡(DFE)校准和可编程的发射器去加重(de-emphasis).

• 支持输出驱动阻抗的自动校准.

• 片上可读出的温度传感器.

• 支持DRAM内建自测试模式 (BIST).

• 支持PHY的各种训练模式: 命令地址训练(CA), 读写时钟对命令地址时钟训练(WCK2CK), 以及读数据训练和写数据训练(支持单个DQ训练).

LC PLL

Ring PLL

High speed, wide frequency range, Low jitter PLL:

Input Clock frequency: 125MHz ~ 500MHz; Output Clock frequency: 5GHz ~ 10GHz;

DLL

Jitter robust, programmable:

Power Supply: 1.0V~1.2V; Frequency Range: 200MHz~1600MHz.

Low Speed PLL

Low Power, small area, wide frequency range:

Power Supply: 1.8V~3.6V; Lock Time: <40us; Input Frequency: 4MHz ~ 25MHz; Output Frequency: 16MHz ~400MHz;

OPA

High accuracy, Multi-Mode OPA with low offset:

Power Supply: 1.8V~3.6V; Rail to rail input: 0V ~ VDD;

Refer to Input offset: +/-3mV (3sigma); Output voltage range: Rail to Rail output; Capacitive load: 50pF.

CMP

Fast response, Multi-Mode CMP with hysteresis:

Power Supply: 1.8V~3.6V; Startup Time: < 7us; Response Time: < 100ns; Comparator hysteresis: 50mv/100mv.

40K internal OSC

Ultra Low Power, support user trimming RC OSC:

Power Supply: 1.8V~3.6V; Startup Time: < 50us; Oscillation Frequency: 40 kHz; Duty Cycle: 45%~ 55%.

8MHz internal OSC

Fast Startup, support factory calibration and user trimming RC OSC:

Power Supply: 1.8V~3.6V; Startup Time: < 2us; Oscillation Frequency: 8MHz; Duty Cycle: 45%~ 55%.